该文章基于B站 2.1.【建库】常规PCB库绘制方法_哔哩哔哩_bilibili

的AD教学及自身学习过程所感而编写

一、创建PCB工程

1、新建工程

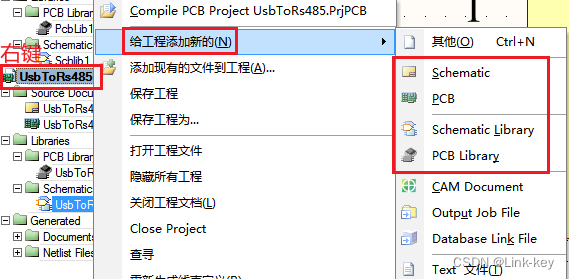

2、给工程添加新文件

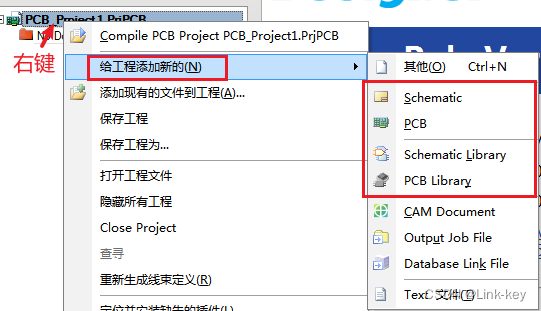

- 右键.Prj……——>给工程添加新的——>前面四个文件加上

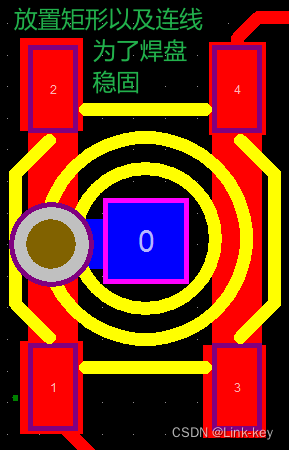

- (1)PCB库文件

- (2)原理图库文件

- (3)PCB文件

- (4)原理图文件

3、 右键.Prj……保存工程——>将四个文件均保存为想要的工程名称

二、建库(以USB TO RS485为例)

1、了解需求

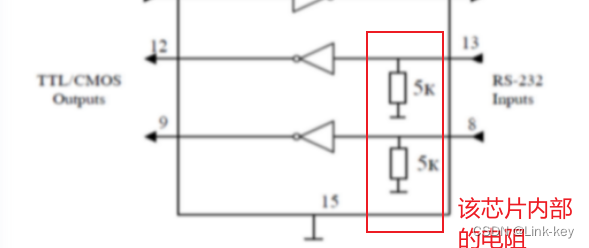

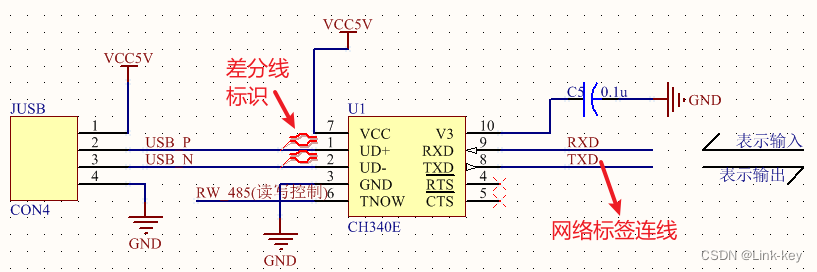

- (1)、需要用到CH340E芯片将USB TO UART

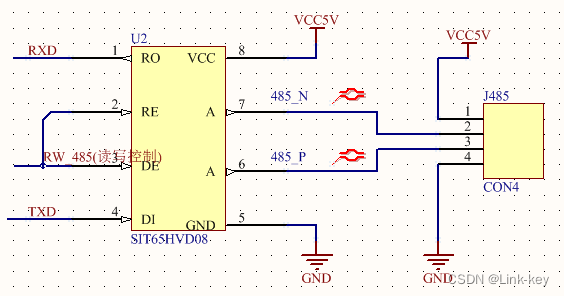

- (2)、用到SIT65HVD08芯片将UART(TTL) TO RS485

2、封装全新元器件PCB

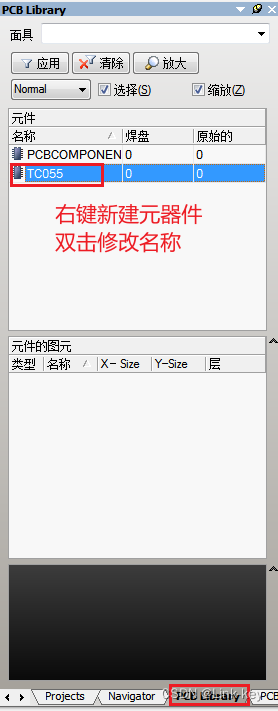

(1)元器件起名

电机进入PcbLib文件——>察看view——>工作区面板——>PCB——>PCB Library——>新建器件取名。

也可以直接左边板块右下角选择PCB Library

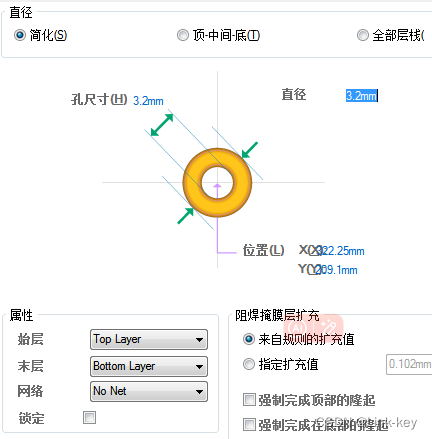

(2)放置焊盘(在Top Layer顶层画(红色))

画该元器件PCB封装(查看芯片手册规格确定焊盘即对应引脚宽度长度)——>确定两两引脚的距离(捕捉栅格Snap Grid)——>栅格属性——>设置步进值间距(为了精细移动)——>焊盘复制粘贴(先选择焊盘点击复制,再点击空白处,出现光标后选择粘贴)——>调整上下引脚焊盘之间距离——>全选右键——>发现相似目标——>拉倒最下面select选择same调整所选引脚焊盘——>Graphical修改y1以Y轴为基准(如果引脚之间Y轴为5,这部分就调为2.5)——>按ctrl+m进行距离测量验收——>编辑——>设置参考——>Center(将整个元件按原点中心摆布)

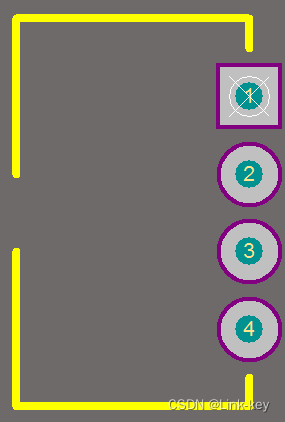

(3)放置丝印(在Top Overlay丝印层画(黄色))

软件底部切换至Top Overlay丝印层——>查看芯片手册发现是3x3mm的长宽——>捕捉栅格Snap Grid)——>栅格属性——>设置步进值间距(设置跳转栅格)为1.5(以中心原点 画一个正方形)——用线画好后改为0.025mm(就是变换栅格让绘制更有参考性更准确)

(4)放置3D外框(在Mechanical机械层(紫色))

放置——>3D元件体——>捕捉栅格设为1.5——>根据元件手册设置总高度为1.1mm ——>围着芯片一圈确定后再确定,按数字3就可以查看3D效果(shift+右键可以旋 转)

3、原理图器件建库

(1)元件起名

进入SchLib文件——>察看view——>工作区面板——>PCB——>SCH Library——>工具TOOl——>新器件——>取名后按确定(末尾带DGK表示其是一个与MSOP8一样的封装)

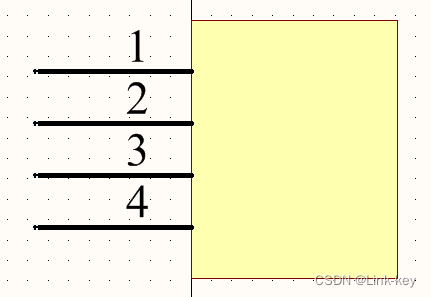

(2)放置引脚(引脚功能名称)

根据芯片对引脚的定义,写相应名称——>是输出型的引脚要在电器类型(Electrical Type)选OutPut——>R\E\表示上面横杆RE——>GND属于Power引脚

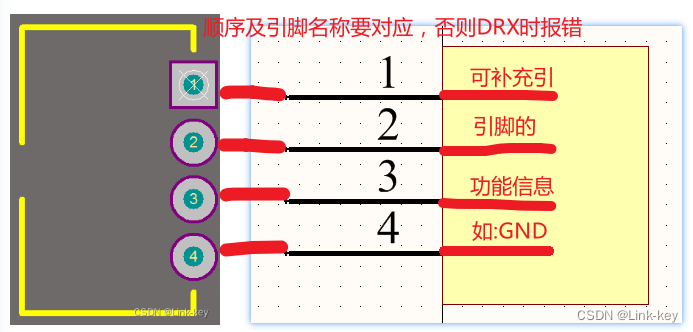

(3)指定原理图元件的PCB封装(注意两者引脚名称要一致,否则DRX时会报错)

双击左边菜单栏SCH Library的器件进入Library Component Properties进行信息录入——>Default Designator集成芯片命名为U?(?以后可变)(器件最上边Text)——>Default Comment为芯片型号名称命名为SIT65HVD08(器件下边的text)——>Description描述直接粘贴第一行芯片手册——>右下角Add——FootPrint——>封装模型名称MSOP8——>浏览选择上面弄得MSOP8得PCB元件

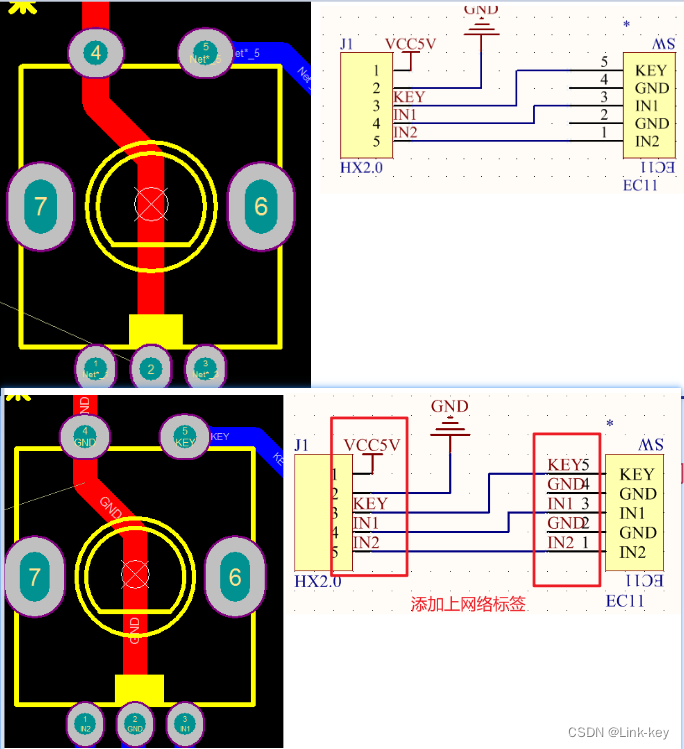

(4)为原理图添加网络标签(网络标签长短要一致,颜色要一致),保证PCB时能够指引连线

三、绘制原理图

1、添加元器件

(1)点击进入原理图——>右侧选择自建库——>*号表示显示所有元器件

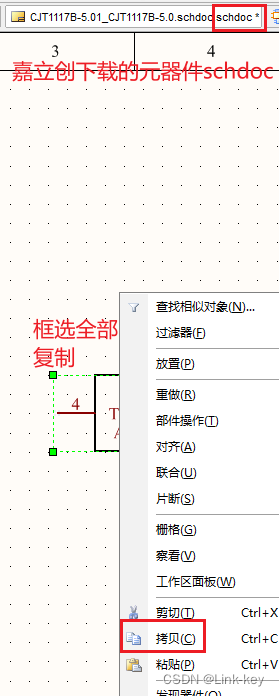

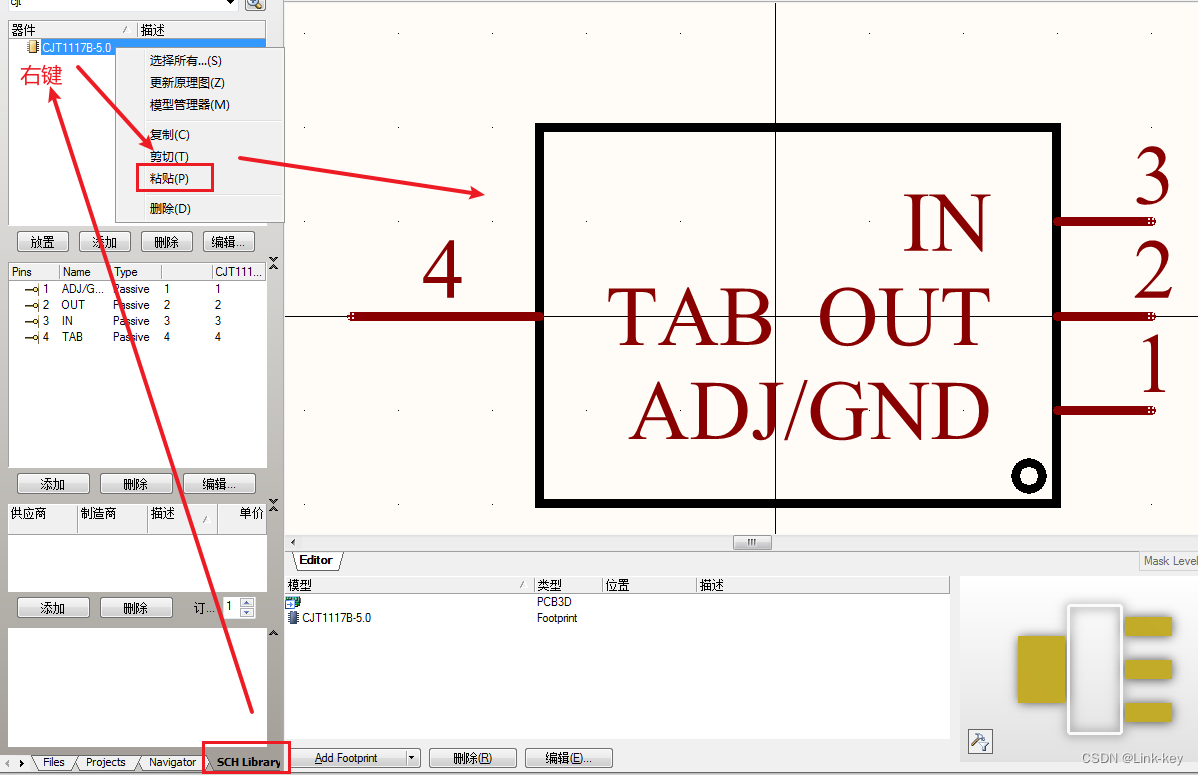

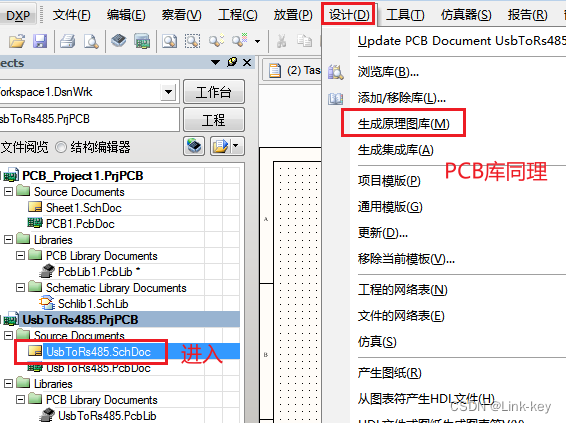

(2)嘉立创EDA导入库——>嘉立创搜索要下载的元器件——>点击数据手册——>下载后打开pcbdoc和schdoc——>设计生成原理图库/生成PCB图库——>去到右侧菜单栏下面的SCH LIB/PCB LIB 没有复制粘贴按键就Ctrl C和Ctrl V到自己的lib中(也可以直接在pcbdoc和schdoc中复制元器件原理图和pcb封装,然后去自己的pcb/sch库新建新的元器件,pcb库直接快捷ctrl C/V,而特别注意原理图需要到pcblibry列表中粘贴才有效)

(3)导入他人文档的自建库——>有lib文件直接打开lib文件,没有则同上转成库文件即可。

注意,导入的PCB封装要删掉一些多余的,否则PCB内绿绿的

2、连接元器件(连线连接元器件(正常连接) 网名连接元器件(线连不过去) 示意标识连接元器件)

- a、放置——>网络标号net Lable——>给差分线标上USB_P/N

- b、放置——>指示——>差分对(给USB_P/N布上差分线标识符)

- c、放置——>指示——>Generic No ERC(给空引脚放上×,让编译时不让悬空脚报错)

- d、放置——>绘图工具——>Line——>可以选择线按空格画半箭头线表示输入输出

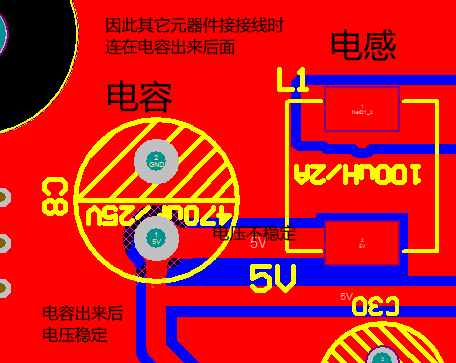

- e、去耦电容相当于水池,给输入端平稳供电流,不至于有很大的波动(接口电容要靠近接口|去耦电容要靠近芯片供电引脚并且容值越小的电容,应该离管角越近)

注意点:

原理图中网络标签不仅仅标识符字符串要对应,延伸出来的颜色线也要一致

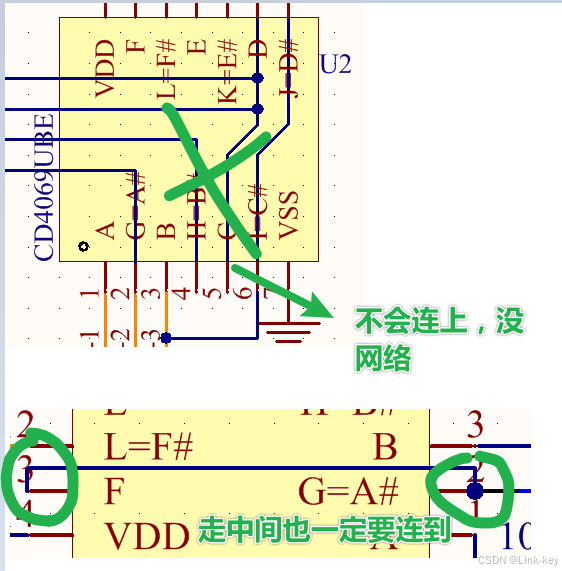

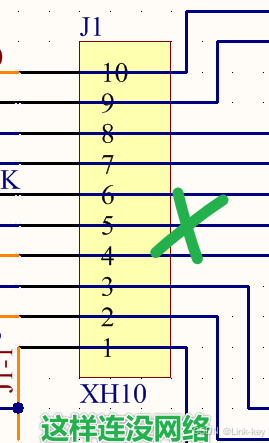

原理图走线不能走内部,就算走也要连上

3、元器件批量编号

Tool工具——>注解——>左侧选择想要标注元器件编号的原理图——>更新更改列表——>接受改变——>执行更改

4、检查原理图

右键Project中的.PrjPcb原理图——complite编译——>没有错误的话,只有警告是不会弹出message的

四、绘制PCB

原理图转PCB,需要网表进行传递内容(对于软件来说,你的引脚叫什么与他完成PCB转换无意义,他只管传递连接信息就可以了)

(1)传递器件信息(编号、封装)

(2)网络(网名、包含引脚)

(3)模型和属性(器件的模型、网络的属性)

设计——>工程网络表——>protel(元件封装)——>右侧菜单栏出现新的文件.NET

]

[ ——一对方括号表示一个元件

C3 ——名称

C0402 ——封装库名字

0.1u ——基本属性

( ——网络用小括号

VCC5V ——VCC5V的网络 包含以下引脚

C1-1 ——C1的一号引脚

C2-1

C3-1

C4-1

J485-1

JUSB-1

U1-7

U2-8

)

1、导入原理图到PCB图中(涉及软件网表自动转换)

- 点击进入原理图文档——>设计第一个——>updata PCB DOC——>执行更改——>查看有没有都add成功——>完成

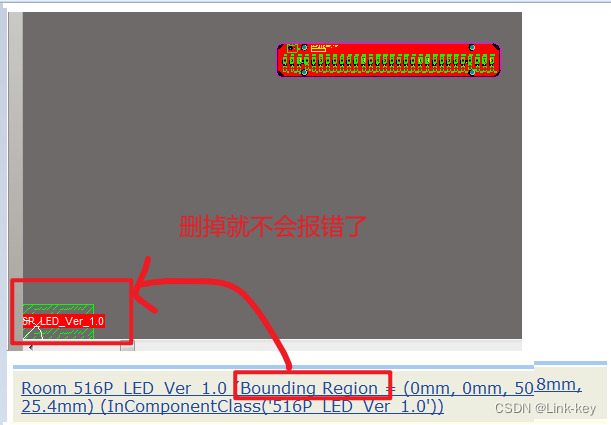

- 可以看到PCB文档下有一个红色框框Room,一般都是使用点阵还有很多独立led控制器之类高度重复性布局,则需要,不然一般删除。

-

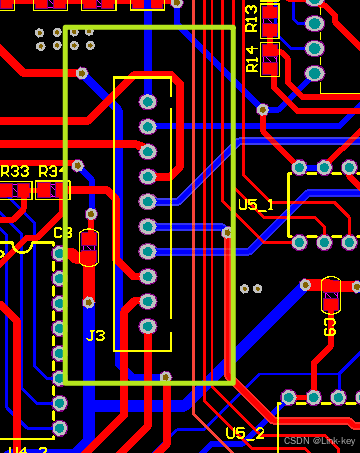

原理图转换为PCB后,进行元器件布局时,先把所有的丝印缩小放在器件中间进行移动,方便布局。 AD中如何批量更改丝印文字大小_ad批量修改丝印大小-CSDN博客

2、建立规则(加工厂的设计极限+个人绘图习惯)

- 板厚 0.8、1.0、1.2、1.6、2.0mm

- 走线厚度 0.1mm

- 钻孔内径、外径 0.2mm、0.45mm

- 走线间距 0.1mm

- 铜厚 1oz、2oz

- 丝印字符 0.8mm

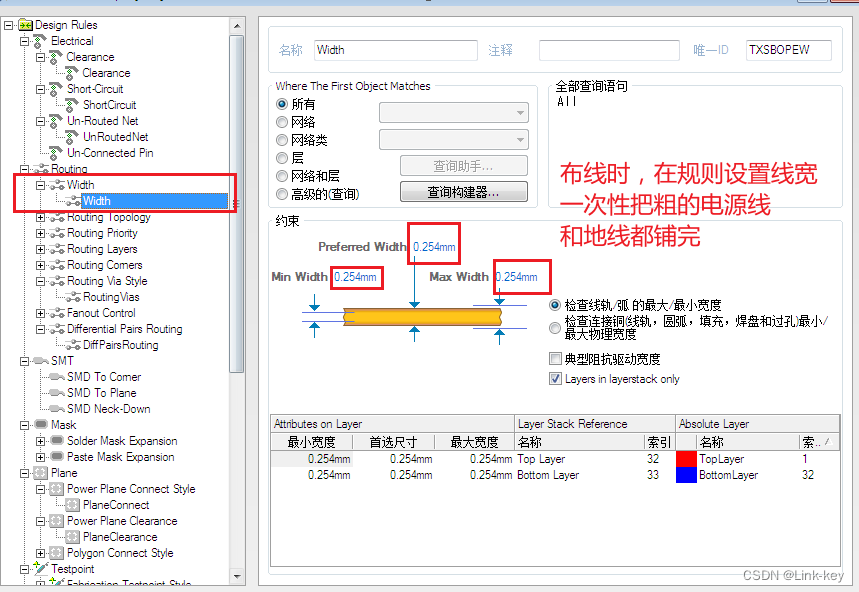

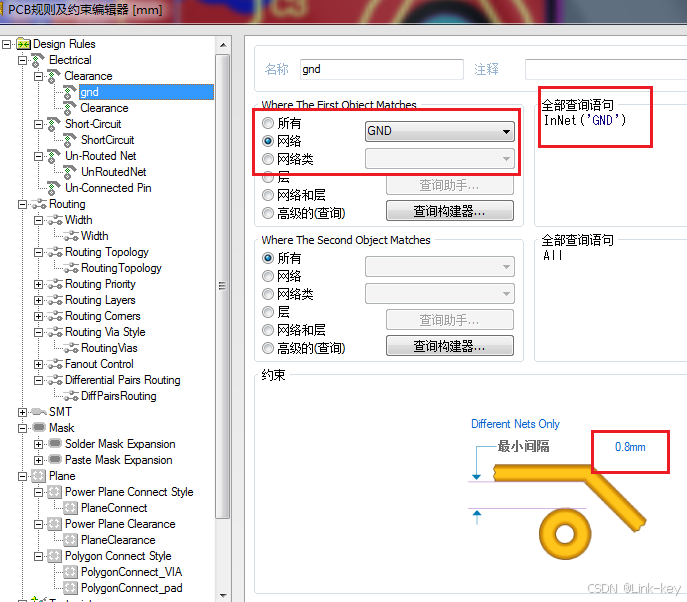

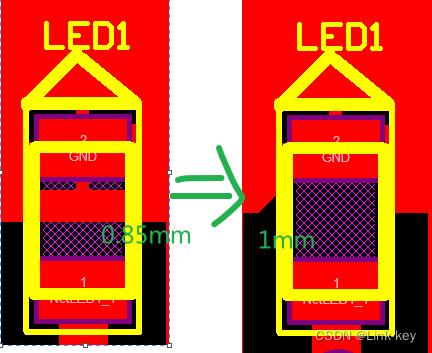

- Desgin设计——>ruler——>Electrical电气规则——>Clearance走线间距——>最小间隔改为0.1mm ——>Routing——>Width线宽——>Min/Prefer都是0.1mm,max填多大都可以填个2mm——>Routing Vias——>左边过孔直径0.45\2\0.45mm——>右边过孔孔径大小0.2\1\0.2mm——>Differential Pairs调差分线(RS485有两条差分线A\B)——>0.1\0.1\1mm Plane——>PologonConnect(铺铜)——>Direct Connect不要铺铜空气间隙——>PlaneClearance——>四层板才会选这个规则,两层板不需要

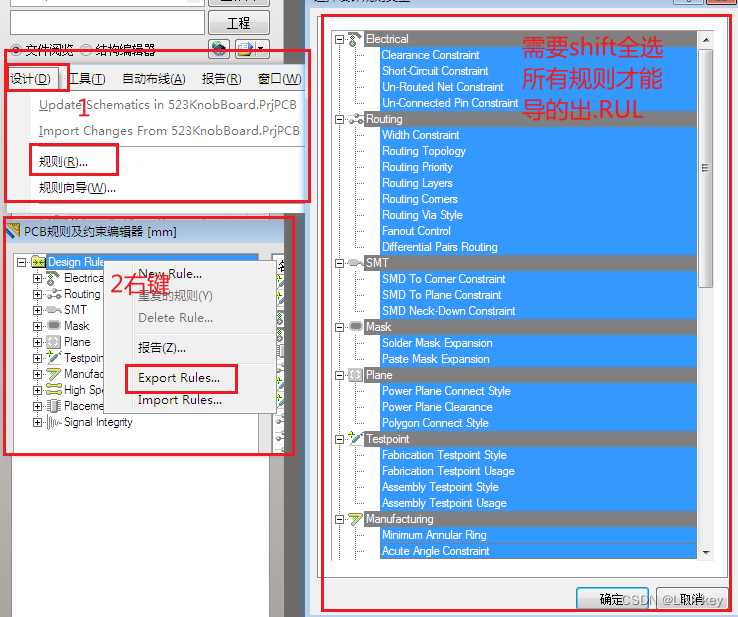

3、规则导入与导出

右键点击Desgin Rule——>Export Rule——>导出规则成一个文件.RUL(重命名)——>或者把他的工程拷过来删干净器件导出规则(获取PCB绘制规则)

4、规划板子大小

(1)可导入CAD的xdf格式图

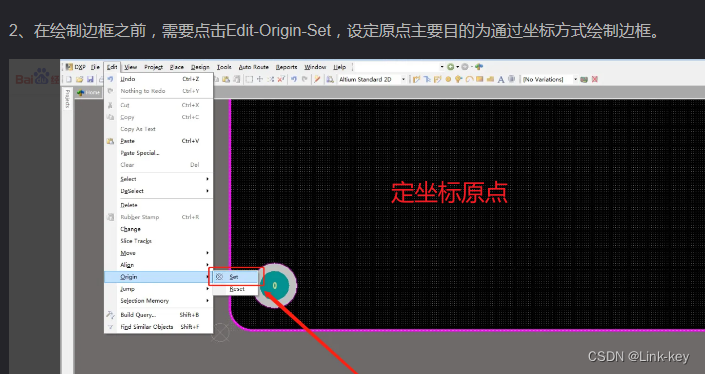

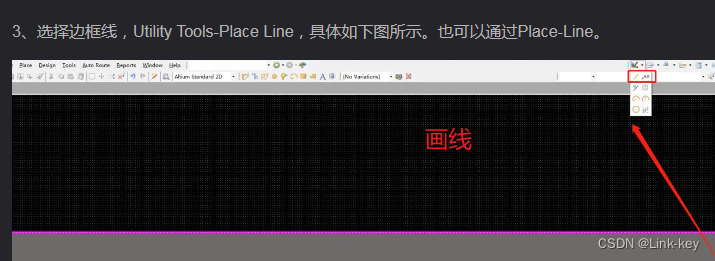

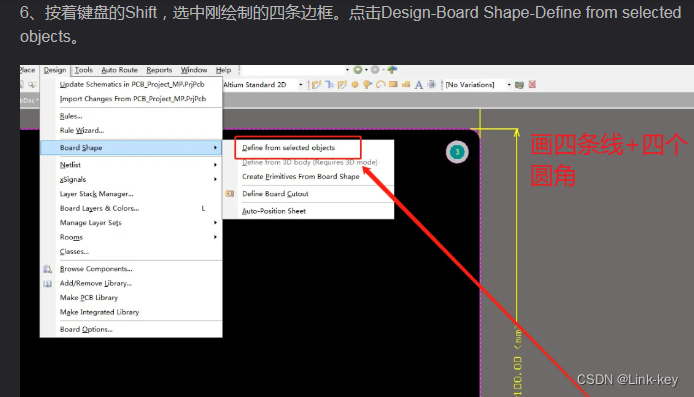

(2)要么只能自己画:

参考站内文章: AD绘制PCB时,如何定义电路板大小以及尺寸标注_ad中如何设计pcb板大小-CSDN博客

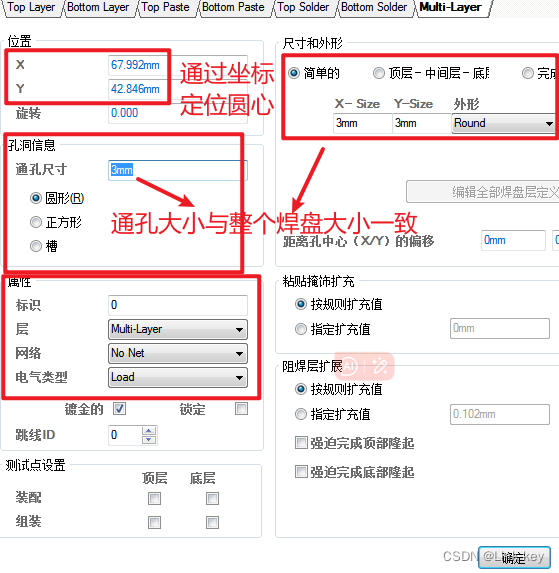

(3)定位固定孔

a、用过孔作为固定孔

b、焊盘作为固定孔

c、划分为机械层作为固定孔

5、器件布局

- a、左键按住器件不动时,才能按空格旋转器件

- b、当组合键不好用时,调成纯英文输入法即可

- c、快捷键L打开板层和颜色设置,去掉一些其他层的显示,让布线时更清爽一些

- d、快捷键L打开第二个选项卡显示和隐藏设置——>string串隐藏掉

- e、有时PCB线步不好,就要回原理图改pin,再重新导入原理图,直到布好

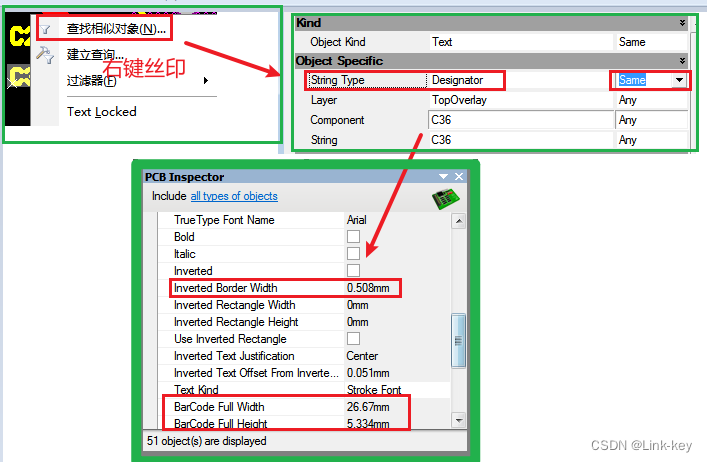

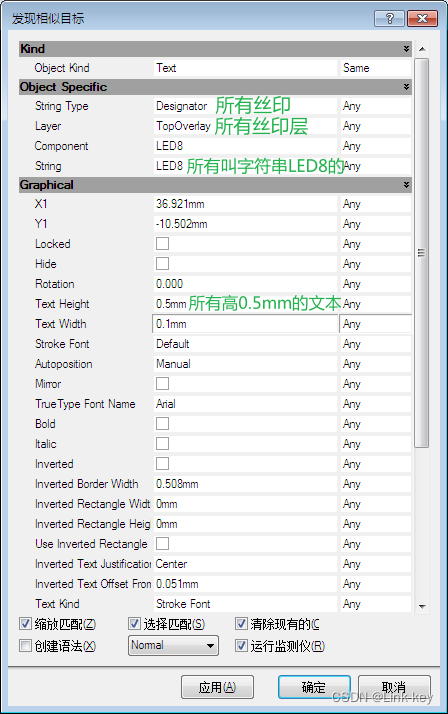

先将所有元器件丝印变小,方便布局和移动:

右键某丝印——>查找相似对象——>选择可以连接到其他相似丝印的选项改为same——>点击确定进行修改想要修改的内容(层级/角度/方向/大小等)

6、布线

- 布线公认规则:

- 1、先布模拟信号线,容易受到干扰,要尽量短

- 2、布高速信号线,容易受到干扰,也容易干扰别人,要尽量短

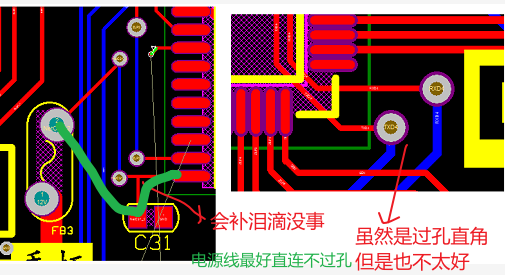

- 3、布电源线/地线(防止后期修板因铜过多难吸过孔的锡),走其他线(哪个方便走哪个)。电源线与地线,最好为1.5mm宽,电源线尽量不要走过孔,而且能短就短。

-

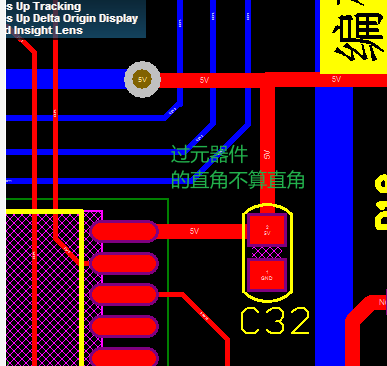

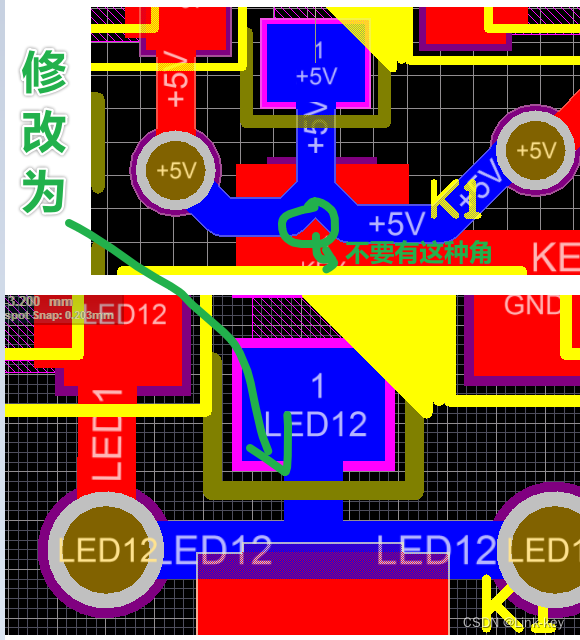

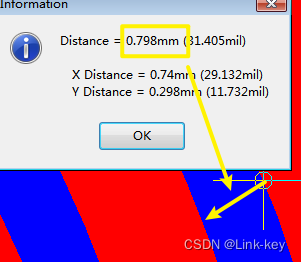

- 4、走线时,避免直角边,不要锐角,钝角转弯,然后线与线之间最好为0.3mm宽,可用报告——>距离测量来测量线与线的距离;

- 5、电容,电阻,与芯片引脚之间,一定要一条线连着,不要过长,不然电容就没作用了。单片机走线开始可以细,但也要跟焊盘粗细一致

- 6、高频信号线互相不要挨那么近,就算不是信号线,也不要挨很近走长线,走长线会等同于多加了个电容,互相要尽量分来些距离,输出线一定要大一些,比如电机的输出线0.6

- 7、T字型过元器件走线没问题,而且最后有泪滴,可以有弧度。

-

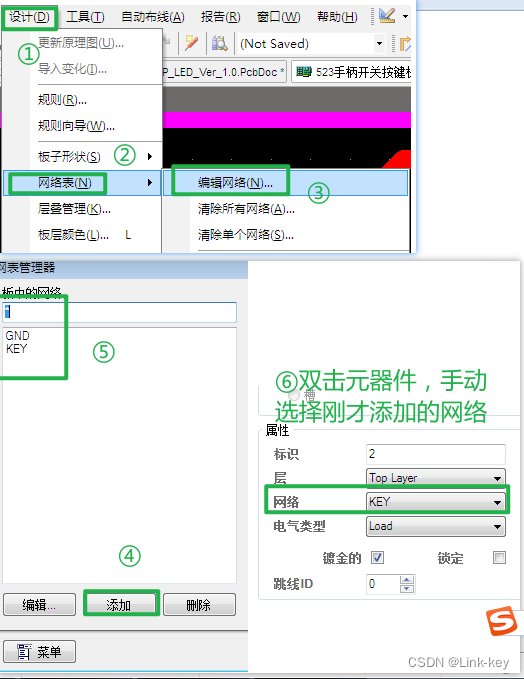

- 8、对于一些没有网络的元器件(过于简单未画原理图导致没网络),手动添加网络上去,避免规则检查时报短路错误,还要注意是否有残余线没有标识到统一的网络,否则也会报短路错误

- 9、电压连线中,一点都不能一样,12V不能连到+12V上去,必须要名字一致(实际使用不影响但规则检查会错误)

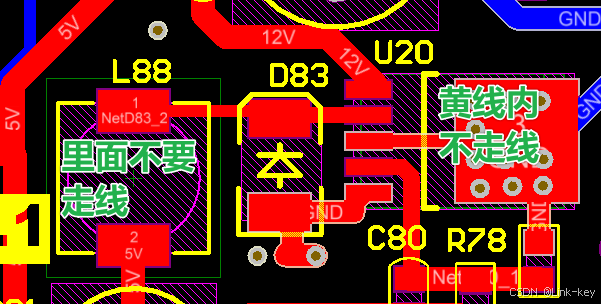

- 10、电感里面和一些元器件封装注意不要走线,因为器件会紧紧压着标明,若破损则会误触

-

- 11、布线时不要一会粗一会细;对于输出线1mm,电源线1.2-1.4,地线1.2-1.4,可以加大加粗。

- 12、布线不用布到边缘,预留丝印大小宽度空间,还有螺母螺柱固定孔也要有一定距离

-

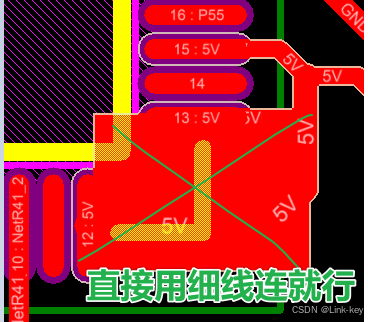

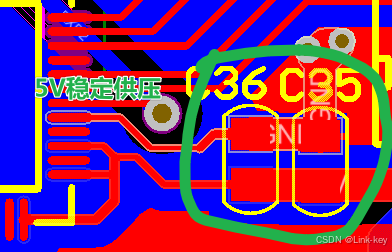

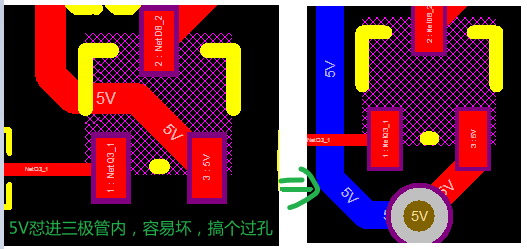

13、单片机的5V不能连铜皮布,焊接不好焊,铜皮冷却块,直接细线连就行

-

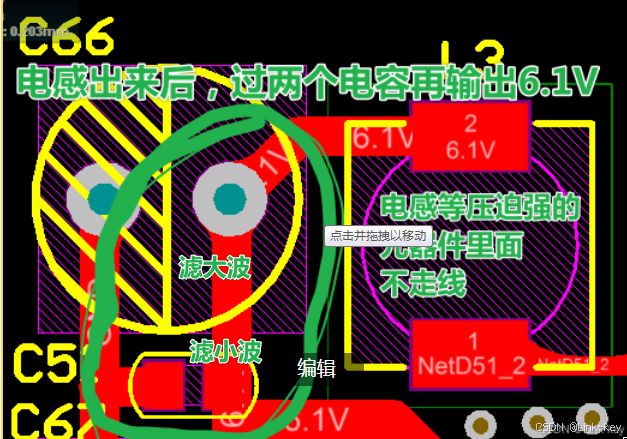

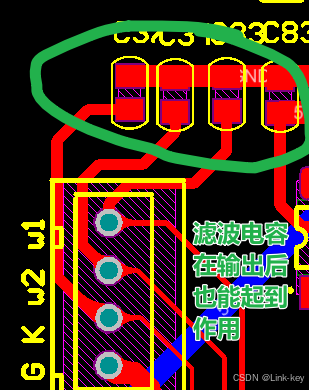

14、一般来说,对于过滤电容,最好经过电容后再输出(电源线特别需要,即避免岔路放电容,放主路),一些其他例如编码器开关则可以不用必须经过。

15、单片机供电过滤电容不要放太远,要挨着近一些

16、单片机里面加个过孔GND,稳一点

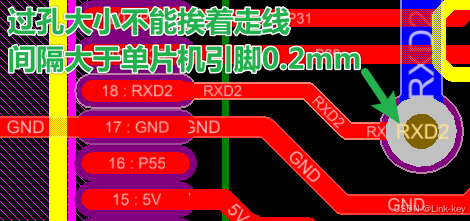

17、过孔不要紧贴线

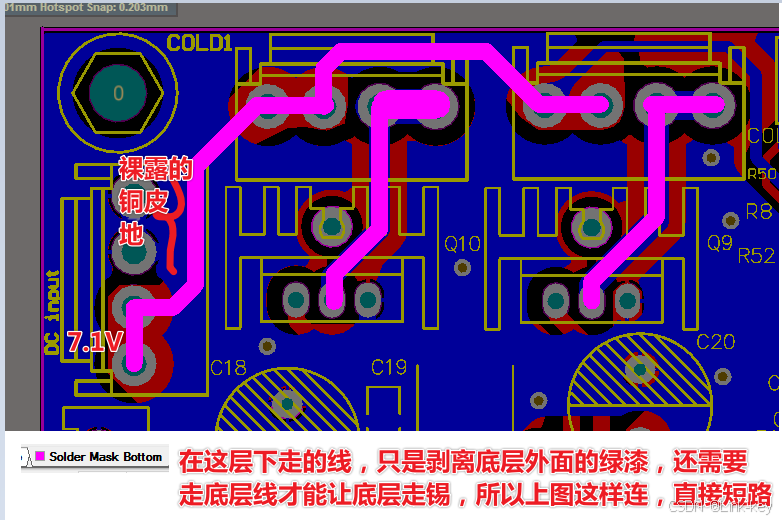

18、为大电流增加锡,可在底部漏出“开窗”,但要记得露的是走的那条线,不是铜皮

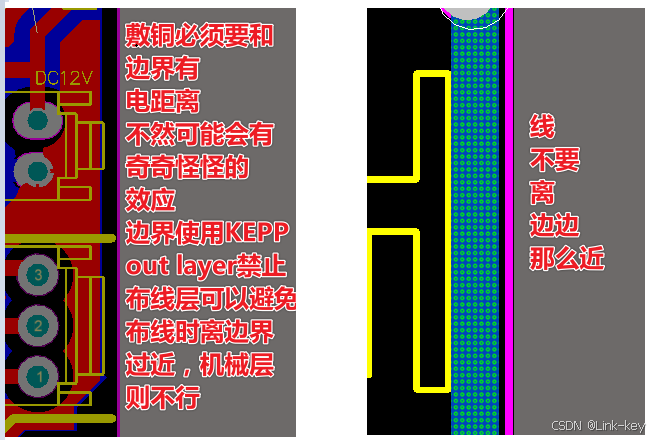

19、边界布线不要距离边界太近,敷铜也要留点距离

20、座子不要放线路板中间,要放边边,这样稳一点,对于一下EMC电路,座子放中间可能会影响其他线路

一些走线不好走时,按住ctrl+shift+空格,改变布线类型,由45度转角变为走曲线,走无角度限制线等

- 线类:

- 1、 交互式布线(一次只能拉出一根线)

- 2、 交互式布总线(有总线时使用到)

- 3、 交互式布差分信号线(一次出两根线,在原理图时就定义了是差分线所以能出两条线,按Tab修改线宽0.1mm,过孔内径大小0.2mm,过孔外径0.45mm)

- 4、布485的信号线,速度有115200,——>按住shift再按空格可以把线变成弯线——>走线时按空格也能改变朝向——>尽量不要走线为直角线(虽然在串口低速上直角和弯角辐射没有差异但是习惯要养成)

- 5、连接地线(放到底层上一起赋铜)——>也改为0.3粗——>连接走线,到想要过孔的位置按住键盘*号,就可以过到第二层(或者可以按住shift按住Ctrl再按滚轮可以切换层数)——>若要过孔就在引脚上(高端产品为节约空间),则可能吸焊锡,出现虚焊,那么就需要加工厂搞过孔塞树脂

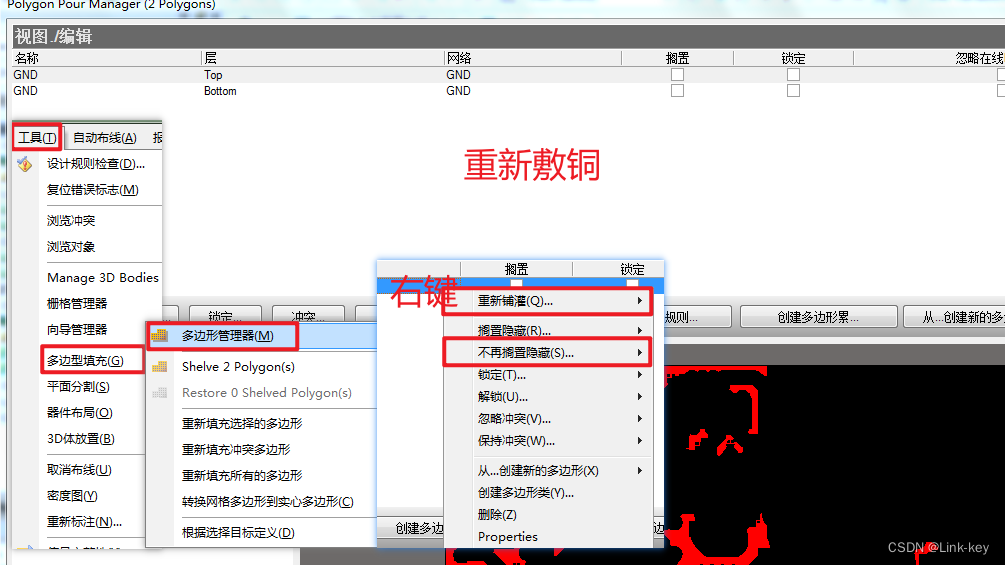

7、铺铜

铺铜前先让每条线搞泪滴:工具——>泪滴,让每一条走线转折处有圆弧。

(1)顶层作为5v电源铜层(一般两层都为GND层)

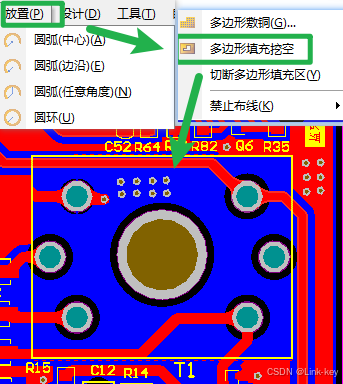

按住Ctrl点击5V焊盘使得连接5V的网络线高亮——>放置place——>Polygon Pour——>起名该层铜皮name叫VCC5V(目的是因为其有很低的电阻,那么5V在这上面能够很好的供电)——>Connect to net连接网络选VCC5V——>Top Layer——>Pour Over All Same Net Objects(将所有同网络名的覆盖)——>光标变成十字——>从输入铺到输出——>覆盖到所有5V的VCC引脚——>修改调整好后要重新铺桐右键铜皮——>Polygon Actions多边形操作——>Repour All/Selected重新填充(铺桐快捷方式:右键桐层点Y再点R)——>选择交互式布线连接电源线——>修改线宽为0.3(电源线要宽一点)

(2)底层作为GND地层

布地层——>Place——>Polygen Pour——>起名该层铜皮name叫GND——>Connect to net连接网络选GND——>Bottom Layer——>Pour Over All Same Net Objects(将所有同网络名的覆盖)——>光标变成十字——>从输入铺到输出

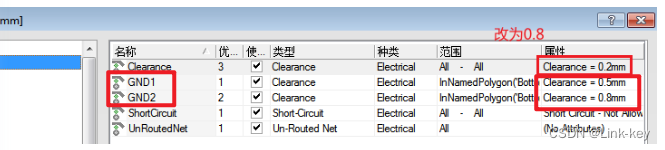

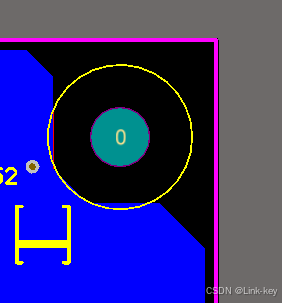

(3)敷铜技巧: 所有的GND网络最好都连在一起,避免大电流导致连GND的十字连接顶不住 ;敷铜时将铜与铜、铜与线之间的间距搞成0.8(若铜皮会穿过元器件中间,则加大至1mm),铜皮不会全部连成一片(对于板空间很大的来说,线宽点好),然后敷完铜后避免设计规则DRC报错,再改回0.2;

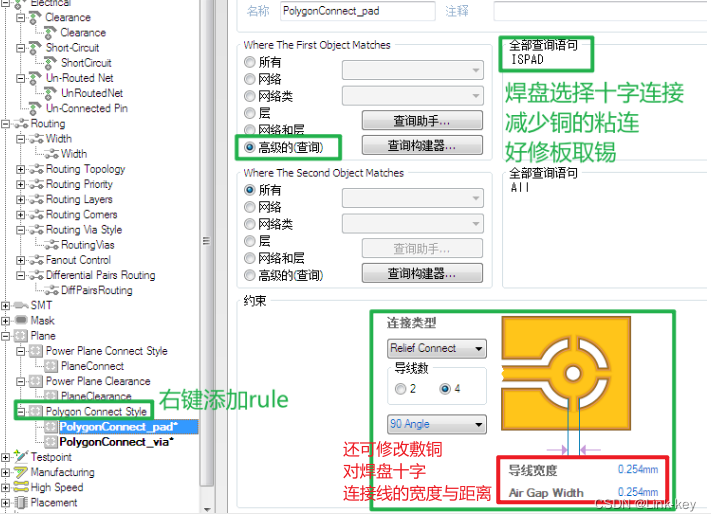

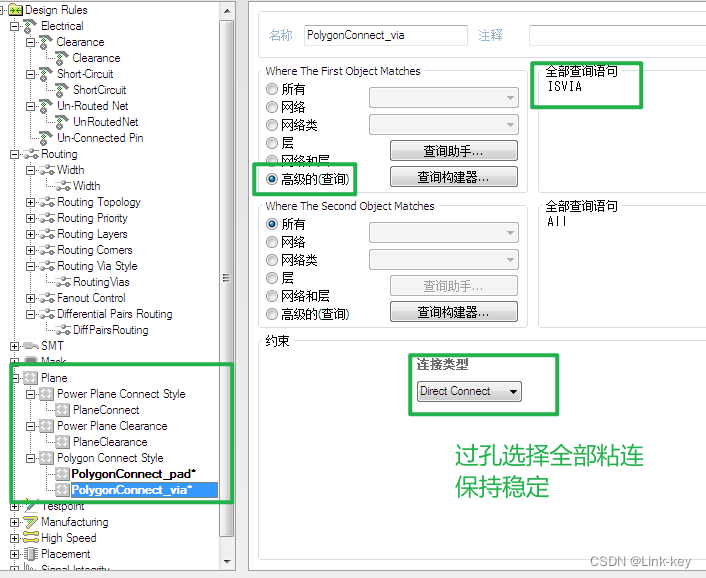

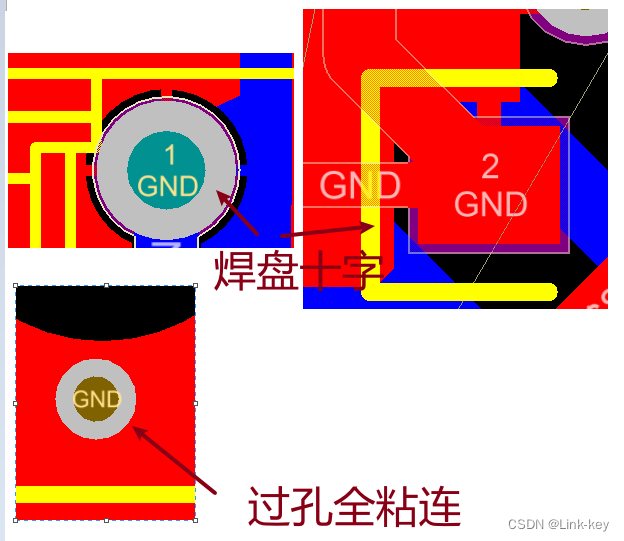

区分敷铜对焊盘(十字连接,避免过多铜连接导致锡难焊和取)与过孔(全粘连)的连接

【原理】

如果所有GND信号的覆铜都是使用 Direct Connect 方式的话,手工焊接的时候会出现GND焊盘难以焊接的情况, 由于连接到大面积的覆铜导致散热较快,以致温度下降难以焊接,这时候使用 Relief Connect 会比较好。但是过孔GND的连接使用 Direct Connect 会更好,降低地线阻抗,也好看一些:

【电路设计】AD多样覆铜连接方式共存_ad设置过孔与覆铜全连接-CSDN博客

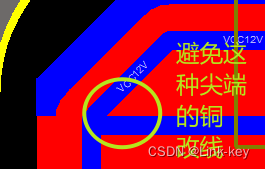

双击铜皮,将当铜……移除颈部,宽小于改为0.6mm,避免顶端过尖,导致尖端放电

若这样改不了,只能改线的走线,或者放一个过孔,避免尖端铜

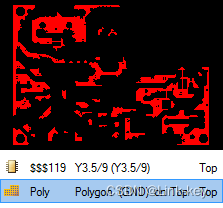

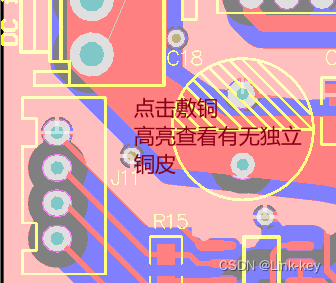

(4)检查铜皮有无独立GND铜皮网络(即没有与板上TOP及BOTTOM层GND铜网络连在一起)

(5)螺丝附近不敷铜,如果被螺丝磨,弄到里面铜皮,再接触到其他东西就不好了。

(6)在高频电路里(例如RF发热)变压器不敷铜(即铜皮不覆盖它),在低频电路微电中可以敷铜,但最好还是不敷。

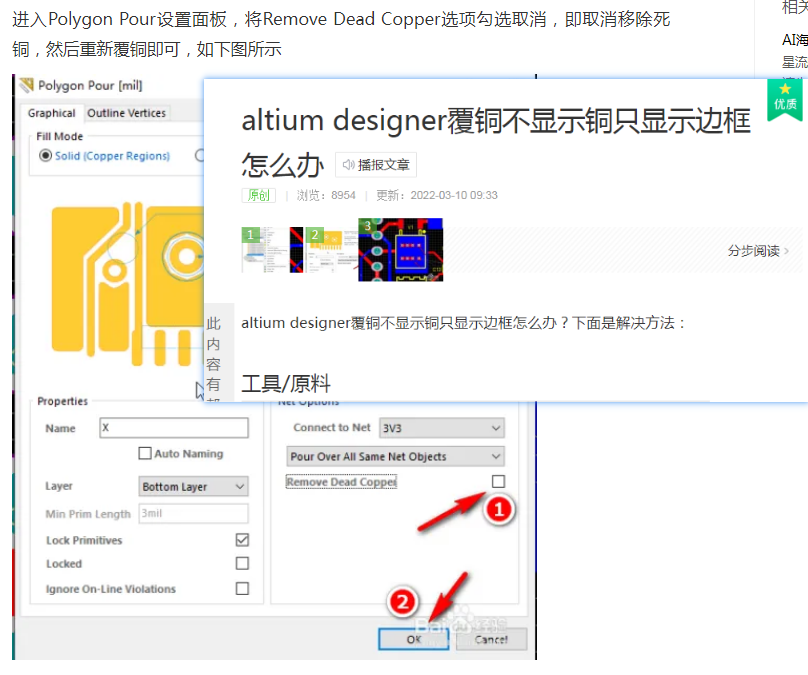

覆铜遇到的问题:

8、规则DRC检查

(1)操作流程

- 工具Tools——>Design Rule Check——>左下角Run Design Rule Check——>查看总的违反规则Summary:

- 1、 Silk to Silk 0.254mm丝印太近

- 2、 Silk To Mask丝印到主焊焊盘这块重叠

- 3、 Minimum Solder Mask Sliver

- ——>Design——>Rules——>Manufacturing(制造)——>Silk To Solder Mask Clearance丝印到焊盘距离搞为0.1——>Silk ToSilk Clearance——>丝印之间为0.1——>MinumumSolder Mask Sliver——>焊盘与焊盘的距离(间距过小没法上绿油且容易焊锡)——改为0——>再去规则检查看看还有没有错误——>按住L将字符打开——>去到错误那点击可以定位到报错位置——>拖动丝印那个字符重新摆放——>属于他的那个元器件会高亮显示,摆到其附近即可不要压到焊盘,放到走线上是可以走线上有阻焊——>在规则检查就没有错误了

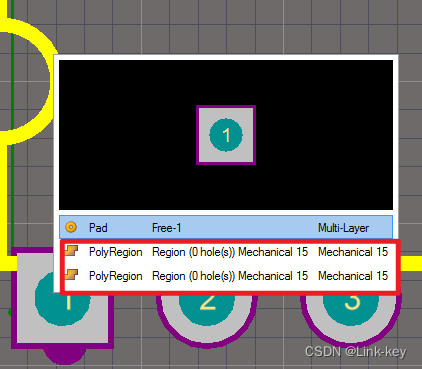

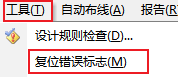

(2)部分DRC规则错误处理

a、Bounding Region

五、导出文件至嘉立创制作

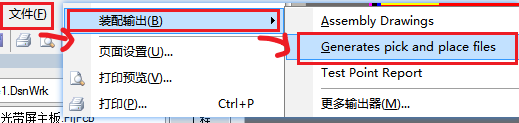

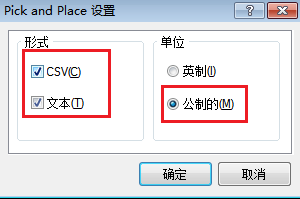

1、元器件位置信息(贴片所需)——在工程文件夹内有一个.csv文件

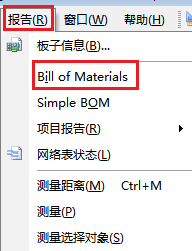

2、输出BOM表——按如下图点击,会有弹窗左下角选择.cvs格式输出

3、再将pcbdoc一起发给嘉立创,就可以贴片打样了

六、AD部分操作

1、 AD批量修改元件所在层级

https://jingyan.baidu.com/article/86f4a73ebd5f9437d7526952.html

2、PCB原理图如何查找原器件?

Edit编辑–>jump跳转–>component器件

3、PCB绿色警告可以在设计选项关闭警告

4、隐藏的铜如何重新显示?

——(搞个快捷方式)——右键上层工具栏——>Customize——>选All——>搜索隐藏多边形/隐藏铺铜/恢复多边形(现在快捷方式设为了ctrl +=/ctrl -_)

其他方式:

5、ctrl左键点击某个元器件,可以让其与其连线高亮显示,ctrl点左键点击两下则取消

七、PCB元器件布局经验

-

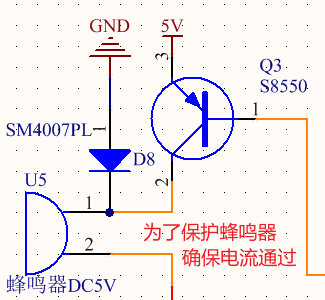

1、反向二极管,保护断电后的反向电流击穿元器件

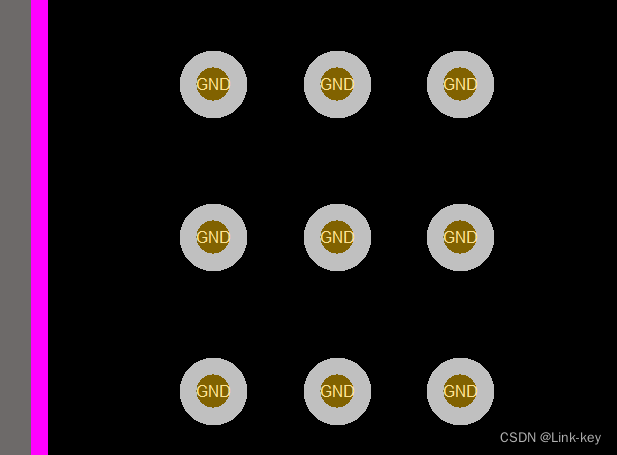

-

2、搞一些GND过孔在板子,保证正反面区域的电荷平衡

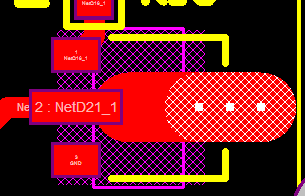

-

3、mos管,控制直流电机,就一个开关作用,就是类似三极管头,但就是要连线多一点才不会报错

4、过孔走电源线保护三极管

5、电容出来后的电压比较稳定

6、不需要连线的元器件最好也连线,以及给与焊盘矩形加固,敷铜时能粘连,防止因为焊接多次导致焊盘脱落(下图还有一个问题会报短路:元器件所有线矩形和焊盘添加上自定义网络避免报短路)

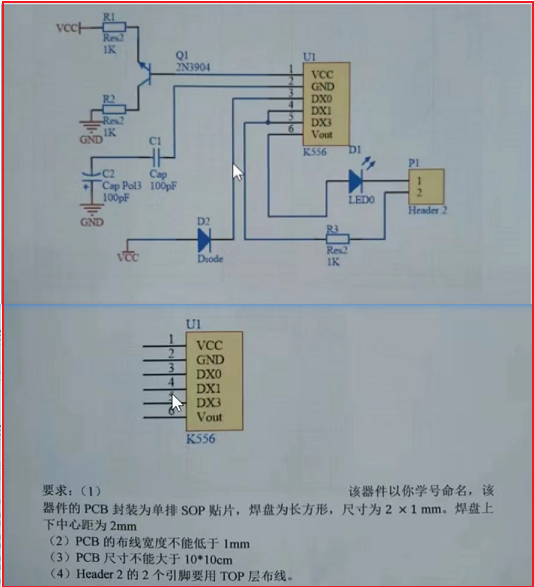

八、作业

九、立创开源项目学习

开源物联网项目ilabel-基于STM32和涂鸦智能平台 - 嘉立创EDA开源硬件平台

十、电路常用单词